臺積電慕尼黑設歐洲設計中心 加速汽車與AI芯片創新

ICC訊 在荷蘭阿姆斯特丹舉行的2025歐洲技術研討會上,臺積電宣布將在德國慕尼黑建立歐洲設計中心,預計于2025年第三季度投入運營。這是臺積電繼臺灣、美國、加拿大、中國大陸和日本之后設立的第十個設計中心。

臺積電表示,選擇慕尼黑而非德累斯頓(其N16和N28制程晶圓廠所在地)的主要原因是慕尼黑更靠近歐洲客戶。該設計中心將專注于汽車、工業應用、人工智能、電信和物聯網等新興領域的優化芯片設計,同時培育歐盟在汽車和非易失性存儲器方面的專業能力,重點推進RRAM和MRAM技術創新,助力行業超越eFlash技術。

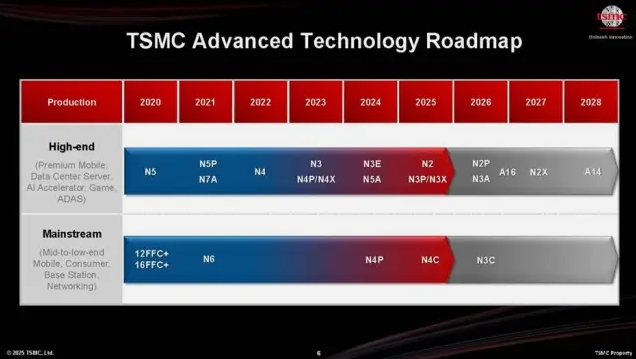

在技術路線圖方面,臺積電更新了A14、A16、N2、N3等制程及3D硅堆疊和先進封裝技術的最新進展。N2制程預計2025年下半年量產,256Mb SRAM平均良率已超90%,其第二年流片數量是N5同期的四倍。N2P制程相比N2在相同功耗下速度提升18%,相同速度下功耗降低36%,計劃2026年下半年量產。

關于3納米制程,臺積電表示N3將成為高產長效節點,截至2025年4月已完成70多次流片。N3P按計劃于2024年第四季度進入量產階段,其衍生產品包括面向客戶端CPU的N3X、提升性價比的N3C以及用于ADAS和自動駕駛技術的N3A。N3A目前正在進行最終缺陷改進,預計2025年通過AEC-Q100 Grade 1認證。

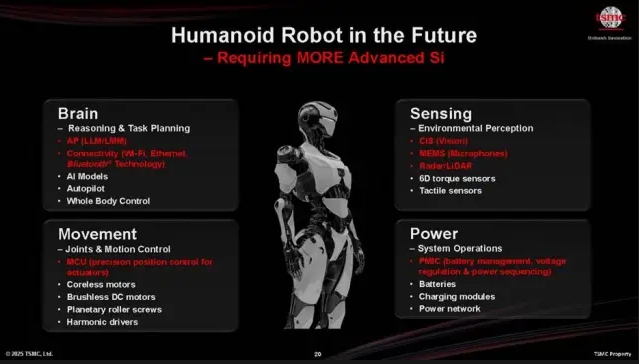

值得注意的是,臺積電指出盡管整體汽車市場疲軟,但自動駕駛領域正在加速采用N4/N3和N6RF等先進邏輯制程。此外,機器人技術將成為繼AI之后的下一個前沿領域,推動對更先進硅芯片的需求。

為應對這些高端應用,臺積電還介紹了其在2024年12月舊金山IEDM會議上提出的互補場效應晶體管(CFET)設計。通過垂直堆疊nFET和pFET,CFET實現了近兩倍的密度提升,其48納米柵極間距的CFET反相器創下世界最小紀錄。

本文作者Nitin Dahad是《EE Times》總編輯,擁有電子工程背景,兼具工程師、記者和企業家多重身份,曾參與多家半導體公司創業及政府科技推廣工作。

本文地址:http://www.wwwhao6v.com//Site/CN/News/2025/05/28/20250528021155679043.htm 轉載請保留文章出處

關鍵字:

文章標題:臺積電慕尼黑設歐洲設計中心 加速汽車與AI芯片創新

2、免責聲明,凡本網注明“來源:XXX(非訊石光通訊網)”的作品,均為轉載自其它媒體,轉載目的在于傳遞更多信息,并不代表本網贊同其觀點和對其真實性負責。因可能存在第三方轉載無法確定原網地址,若作品內容、版權爭議和其它問題,請聯系本網,將第一時間刪除。

聯系方式:訊石光通訊網新聞中心 電話:0755-82960080-168 Right

- · 華為ICT大賽2024-2025全球總決賽收官:AI賦能教育轉型,助力ICT人才培養

- · 2D Photonics獲2.5千萬歐融資 石墨烯技術革新AI通信

- · Crusoe啟動全球最大AI數據中心集群建設 將部署多達40萬塊NVIDIA GB200超級芯片

- · BAT資本開支激增 AI與算力競賽白熱化

- · 百度2025年Q1財報:AI云收入激增42%引領增長

- · 華為提出“1+5+X”萬智互聯新圖景,攜手產業共贏移動AI時代

- · 新加坡電信以15億美元出售了Bharti Airtel部分股份

- · 英偉達簽下沙特1.8萬枚AI芯片大單

- · 歐億光電攜八大應用場景解決方案亮相武漢光博會2B14

- · Adtran通過動態AI網絡云解決方案提升DCI能力

- 設置首頁 | 光通訊招聘 | 企業搜索庫 | 廣告服務 | 聯系我們 | 保護私隱 | 公司介紹

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 訊石公司 www.wwwhao6v.com版權所有 粵ICP備12008183號-1