歐洲押注300毫米晶圓異質集成技術爭奪半導體主權

ICC訊 對于Fraunhofer IZM-ASSID晶圓級系統集成負責人Manuela Jungh?hnel而言,半導體主權不僅關乎芯片制造,更在于封裝、堆疊與部署能力。在2025年6月17日德國德累斯頓舉行的"薩克森硅谷日"活動上,她闡述了歐洲如何通過300毫米晶圓上的3D異質集成技術,重新奪回先進半導體封裝領域的戰略地位。

在接受《EE Times Europe》獨家專訪時,Jungh?hnel揭示了團隊如何彌合高端研究與工業應用之間的鴻溝。其背后是一套融合公共資金、頂尖研究與產業化的歐洲創新模式。

構建覆蓋AI至量子的本土生態

Fraunhofer IZM-ASSID坐落于前奇夢達工廠舊址,與GlobalFoundries隔街相望,毗鄰博世、英飛凌及在建的ESMC超級工廠。這個成立15年的機構專注于300毫米晶圓異質集成——這項技術此前在歐洲尚無工業級應用。

"我們不與大規模晶圓廠競爭,"Jungh?hnel表示,"而是為需要小批量、高性能系統的企業提供先進封裝與3D集成服務。"隨著AI推理向邊緣端遷移、量子計算需要特殊互連,以及功耗與散熱成為芯片關鍵指標,將傳感器、邏輯單元、存儲器和光器件緊密集成的能力已具有戰略意義。

團隊打造了"工業級試驗線",核心技術包括硅通孔、微凸塊鍵合和重分布層。Jungh?hnel強調:"我們引入了全自動化設備、晶圓廠級潔凈室和工藝控制系統,這在研究機構中很罕見。"

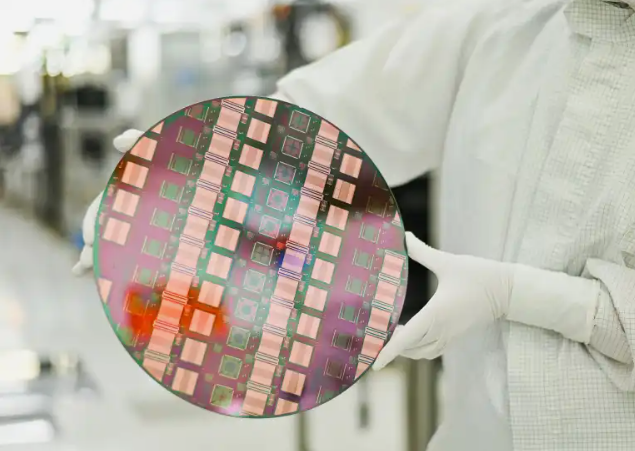

帶有流體通道的300毫米硅中介層晶圓(用于主動冷卻)(Fraunhofer IZM-ASSID,攝影:Silvia Wolf)

技術路線:從10微米間距到量子低溫封裝

當前研究重點包括:將互連間距縮小至10微米以下,開發嵌入微腔與直接液體冷卻的轉接板技術,以及用于超高密度集成的混合鍵合工藝。在量子計算領域,團隊正為德國"QSolid"項目開發可在毫開爾文溫度下工作的超導封裝方案,旨在用高密度低溫互連取代現有數公里長的電纜系統。

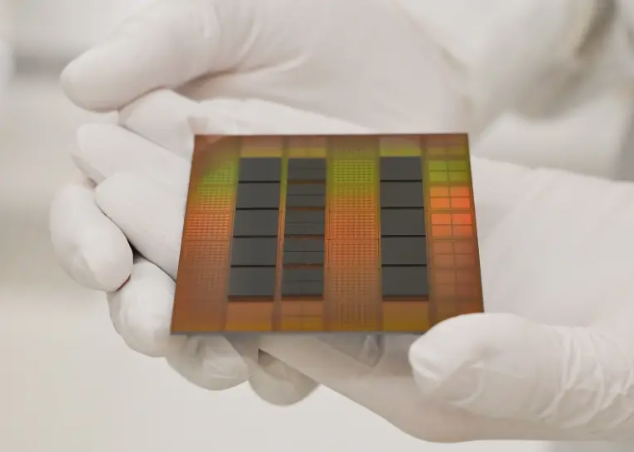

采用10微米間距超細銅混合鍵合接觸的已安裝芯片粒(Fraunhofer IZM-ASSID,攝影:Silvia Wolf)

共享基礎設施戰略

作為《歐洲芯片法案》APECS試驗線計劃的關鍵執行方,Fraunhofer IZM-ASSID將投資9500萬歐元擴建900平方米潔凈室,打造面向初創企業、中小院校的芯片粒系統共享平臺。"與其讓每個實驗室自建300毫米產線,不如集中建設具備工業級可靠性的共享設施,"Jungh?hnel指出。

相較于新建晶圓廠的宏大宣言,Jungh?hnel的觀點更為深刻:主權不僅需要制造能力,更需掌握從封裝到部署的全鏈條技術。在AI、高性能計算與量子技術的競賽中,她認為"芯片互連處才是真正的戰場"。

這場演講沒有產品發布或政策游說,而是展現了歐洲半導體復興的底層邏輯:以扎實的工程技術構建持久競爭力。正如Jungh?hnel所言:"集成不再是瓶頸,而是戰略支點。"

原文鏈接:Europe Bets on Heterogeneous Integration on 300-mm Wafers | https://www.eetimes.eu/europes-strategic-bet-heterogeneous-integration-on-300-mm-wafers/?_gl=1*1wnjzgj*_gcl_au*MzgzNjg2ODEuMTc0NDA3OTI1OQ..*_ga*MTgyNjI4ODkyMS4xNzMyNDk2MTcx*_ga_ZLV02RYCZ8*czE3NTA4OTkzMTEkbzc2JGcwJHQxNzUwODk5MzExJGo2MCRsMCRoMA..

本文地址:http://www.wwwhao6v.com//Site/CN/News/2025/06/26/20250626013155386313.htm 轉載請保留文章出處

關鍵字:

文章標題:歐洲押注300毫米晶圓異質集成技術爭奪半導體主權

2、免責聲明,凡本網注明“來源:XXX(非訊石光通訊網)”的作品,均為轉載自其它媒體,轉載目的在于傳遞更多信息,并不代表本網贊同其觀點和對其真實性負責。因可能存在第三方轉載無法確定原網地址,若作品內容、版權爭議和其它問題,請聯系本網,將第一時間刪除。

聯系方式:訊石光通訊網新聞中心 電話:0755-82960080-168 Right

- 設置首頁 | 光通訊招聘 | 企業搜索庫 | 廣告服務 | 聯系我們 | 保護私隱 | 公司介紹

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 訊石公司 www.wwwhao6v.com版權所有 粵ICP備12008183號-1